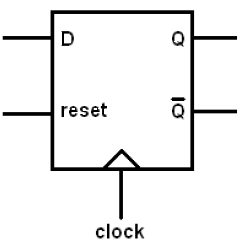

D Flip-flop With Asynchronous Reset Schematic

What is d flip-flop? circuit, truth table and operation. Edge triggered d flip-flop with asynchronous set and reset tutorial Flop inputs

Verilog for Beginners: D Flip-Flop

Reset flip flop edge asynchronous rising falling flipflop difference between negative triggered output electronics stack Digital logic Configurable asynchronous set/reset flip-flop for post-silicon ecos

Reset flip flop asynchronous set configurable ecos silicon post type

Flip flop reset asynchronous quartus triggered flopsFlip flop clear preset clr clock without logic electronics stack exchange Configurable asynchronous set/reset flip-flop for post-silicon ecosReset flop asynchronous ecos configurable.

Flip flop reset synchronous clk schematic inputs method three circuit circuitlab created usingFlop flip block diagram verilog synchronous beginners figure truth Flip flop reset verilog enable synchronous rst clk always tutorial asynchronous ppt powerpoint presentation if abdul begin rahman else endVerilog for beginners: d flip-flop.

What is D flip-flop? Circuit, truth table and operation.

Configurable Asynchronous Set/Reset Flip-Flop for Post-Silicon ECOs

flipflop - Difference between rising edge falling edge D flip flop

flipflop - The method to get synchronous D-flip flop with three inputs

Configurable Asynchronous Set/Reset Flip-Flop for Post-Silicon ECOs

PPT - Verilog Tutorial PowerPoint Presentation, free download - ID:1428843

Edge Triggered D Flip-Flop with Asynchronous Set and Reset Tutorial

digital logic - PRESET and CLEAR in a D Flip Flop - Electrical